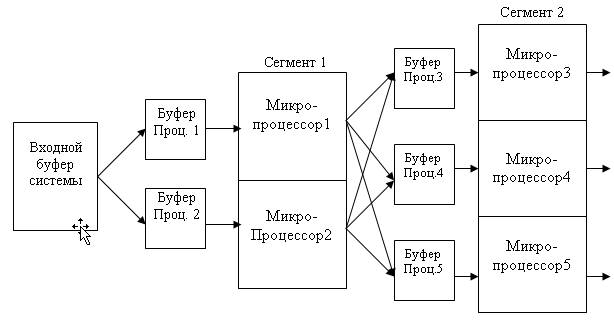

1.Построение структурной схемы модели

В соответствии с техническим заданием, структурная схема модели имеет вид:

Рис.1 Структурная схема модели

2. Описание сети в виде системы массового обслуживания

При решении задач моделирования с помощью СМО процесс анализа связан с исследованием прохождения через эти системы заявок (требований). Эти заявки называются транзактами. Все транзакты являются случайными процессами и при моделировании СМО могут быть известны лишь законы распределения и числовые характеристики этих случайных распределений, т.е. СМО носит статистический характер.

Устройства, в которых производится обслуживание транзактов, называются обслуживающими аппаратами (ОА) или каналами. ОА в совокупности образуют статические объекты. Транзакты называются динамическими объектами. ОА (каналы) описываются в СМО с помощью булевых переменных: «свободно» или «занято» («1» или «0»).

В процессе работы СМО могут возникать очереди. Количество очередей может быть бесконечно или с ограничением. Правила, согласно которым заявки выбираются из очереди, называются дисциплиной обслуживания. Величина, выражающая преимущество на право обслуживания называется приоритетом.

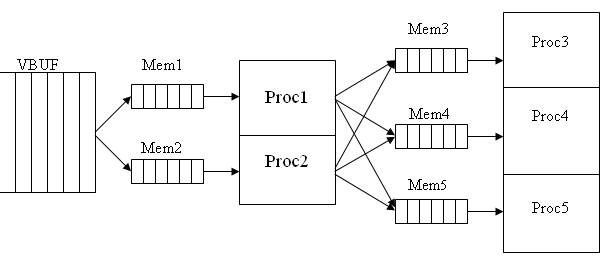

В соответствии с полученной структурной схемой модели, представим её в виде СМО. В нашей модели роль транзактов выполняют пакеты данных приходящих от источников А, В и С. Приоритет этих транзактов, согласно заданию, одинаков. В качестве ОА (каналов) выступают блоки обработки данных.

VBUF – входной буфер системы.

Mem1 – буфер первого процессора, первого сегмента конвейера(Ёмкость-10).

Mem2 – буфер второго процессора, первого сегмента конвейера(Ёмкость-10).

Mem3 – буфер первого процессора, второго сегмента конвейера.

Mem4 – буфер второго процессора, второго сегмента конвейера.

Mem5 – буфер третьего процессора, второго сегмента конвейера

Рис.2 Модель в виде СМО

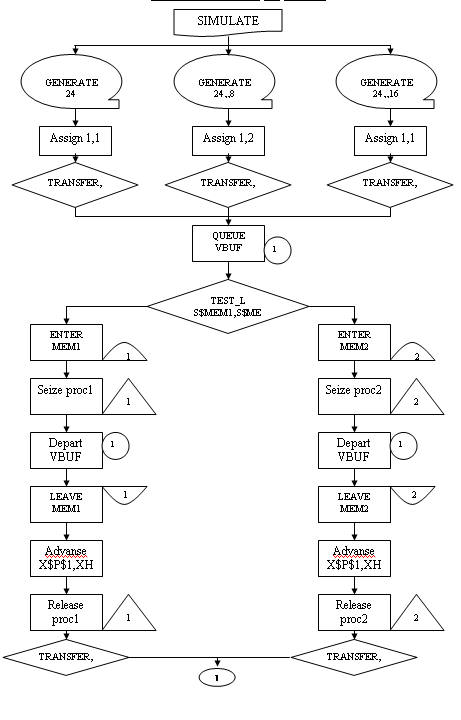

3. Формализация и алгоритмизация задачи

3.1 Алгоритм обработки транзактов

1. Вход транзакта в модель;

2. Вход в буфер системы (VBUF);

3. Переход в буфер первого или второго процессора по критерию минимума входной очереди;

4. Вход в процессор с минимальной входной очередью (если он свободен);

5. Выход из этого буфера;

6. Выход из буфера системы;

7. Занятие соответствующего процессора для обработки;

8. Обработка за время 10-18 мкс (для заявок первого типа) или за 11-23 мкс (для заявок второго типа);

9. Освобождение процессора первого сегмента;

10. Выбор для обработки процессора второго сегмента по критерию минимума входной очереди;

11. Вход в буфер этого процессора;

12. Вход в соответствующий процессор (если он свободен);

13. Выход из буфера соответствующего процессора;

14. Обработка за время 12-32 мкс(для заявок первого типа) или за 20-30 мкс (для заявок второго типа);

15. Освобождение процессора второго сегмента;

16. Уничтожение транзактов.

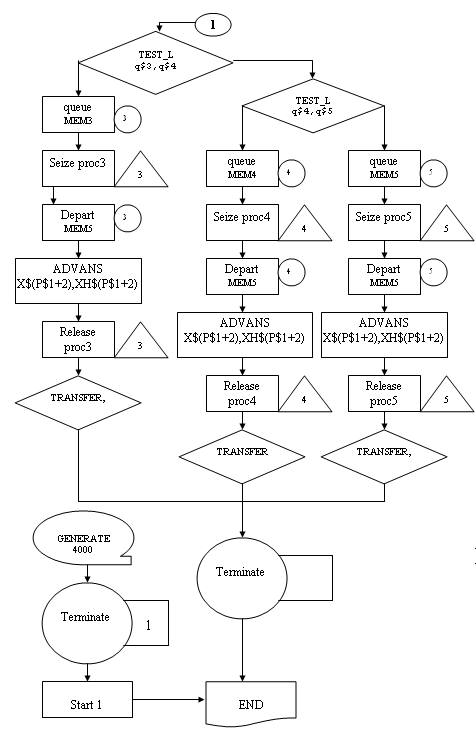

3.2 Блок-схема программы

4. Имитационный эксперимент

4.1 Текст программы

mem1 equ 1 ;символическое и числовое имена буфера проц. №1

mem2 equ 2 ;символическое и числовое имена буфера проц. №2

vbuf equ 1 ;символическое и числовое имена буфера системы

mem3 equ 2 ;символическое и числовое имена буфера проц. №3

mem4 equ 3 ;символическое и числовое имена буфера проц. №4

mem5 equ 4 ;символическое и числовое имена буфера проц. №5

proc1 equ 1 ;символическое и числовое имена проц. №1

proc2 equ 2 ;символическое и числовое имена проц. №2

proc3 equ 3 ;символическое и числовое имена проц. №3

proc4 equ 4 ;символическое и числовое имена проц. №4

proc5 equ 5 ;символическое и числовое имена проц. №5

initial x$1,14 ;определение значений задержек

initial x$2,17

initial x$3,22

initial x$4,25

initial xh$1,4

initial xh$2,6

initial xh$3,10

initial xh$4,5

simulate ;разрешает моделирование

storage s$mem1,10 ; объём буфера проц. №1

storage s$mem2,10 ;объём буфера проц.№2

generate 24 ;генерация транзактов

assign 1,1 ;транзакты 1-ого типа

transfer ,buf ;безусловный переход к строке Buf

generate 24,,8 ;генерация транзактов

assign 1,2 ;транзакты 2-ого типа

transfer ,buf ;безусловный переход к строке Buf

generate 24,,16 ;генерация транзактов

assign 1,1 ;транзакты 1-ого типа

buf queue vbuf ;занятие входного буфера

test_l s$mem1,s$mem2,prod1 ;определение min очереди

enter mem1 ;вход в mem1

seize proc1 ;занятие proc1

depart vbuf ;покидание входного буфера

leave mem1 ;выход из mem1

advans x$p$1,xh$p$1 ;обработка в proc1

release proc1 ;освобождение proc1

transfer,prod2 ;безусловный переход к строке prod2

prod1 enter mem2 ;вход в mem2

seize proc2 ;занятие proc2

depart vbuf ;покидание входного буфера

leave mem2 ;выход из mem2

advans x$p$1,xh$p$1 ;обработка в proc2

release proc2 ;освобождение proc2

prod2 test_l q$mem3,q$mem4,prod3 ;определение min очереди(+стр. prod3)

queue mem3 ;вход в mem3

seize proc3 ;занятие proc3

depart mem3 ;выход из mem3

advans x$(p$1+2),xh$(p$1+2) ;обработка в proc3

release proc3 ;освобождение proc

transfer,final ;безусловный переход к уничтожению

prod3 test_l q$mem4,q$mem5,prod4 ;определение min очереди

queue mem4 ;вход в mem4

seize proc4 ;занятие proc4

depart mem4 ;выход из mem4

advans x$(p$1+2),xh$(p$1+2) ;обработка в proc4

release proc4 ;освобождение proc

transfer,final ;безусловный переход к уничтожению

prod4 queue mem5 ;вход в mem5

seize proc5 ;занятие proc5

depart mem5 ;выход из mem5

advans x$(p$1+2),xh$(p$1+2) ;обработка в proc5

release proc5 ;освобождение proc

final terminate ;уничтожение транзактов

generate 4000 ;генерация отрезка времени 4мс

terminate 1 ; уменьшение счётчика на 1

start 1 ; установка нач. значения счётчика (1)

end ;конец программы

4.2 Листинг результатов моделирования

LINE BLOCK

1 MEM1 EQU 1

2 MEM2 EQU 2

3 VBUF EQU 1

4 MEM3 EQU 2

5 MEM4 EQU 3

6 MEM5 EQU 4

7 PROC1 EQU 1

8 PROC2 EQU 2

9 PROC3 EQU 3

10 PROC4 EQU 4

11 PROC5 EQU 5

12 INITIAL X$1,14

13 INITIAL X$2,17

14 INITIAL X$3,22

15 INITIAL X$4,25

16 INITIAL XH$1,4

17 INITIAL XH$2,6

18 INITIAL XH$3,10

19 INITIAL XH$4,5

20 SIMULATE

21 STORAGE S$MEM1,10

22 STORAGE S$MEM2,10

23 1 GENERATE 24

24 2 ASSIGN 1,1

25 3 TRANSFER ,BUF

26 4 GENERATE 24,,8

27 5 ASSIGN 1,2

28 6 TRANSFER ,BUF

29 7 GENERATE 24,,16

30 8 ASSIGN 1,1

31 9 BUF QUEUE VBUF

32 10 TEST_L S$MEM1,S$MEM2,PROD1

33 11 ENTER MEM1

34 12 SEIZE PROC1

35 13 DEPART VBUF

36 14 LEAVE MEM1

37 15 ADVANS X$P$1,XH$P$1

38 16 RELEASE PROC1

39 17 TRANSFER,PROD2

40 18 PROD1 ENTER MEM2

41 19 SEIZE PROC2

42 20 DEPART VBUF

43 21 LEAVE MEM2

44 22 ADVANS X$P$1,XH$P$1

45 23 RELEASE PROC2

46 24 PROD2 TEST_L Q$MEM3,Q$MEM4,PROD3

47 25 QUEUE MEM3

48 26 SEIZE PROC3

49 27 DEPART MEM3

50 28 ADVANS X$(P$1+2),XH$(P$1+2)

51 29 RELEASE PROC3

52 30 TRANSFER,FINAL

53 31 PROD3 TEST_L Q$MEM4,Q$MEM5,PROD4

54 32 QUEUE MEM4

55 33 SEIZE PROC4

56 34 DEPART MEM4

57 35 ADVANS X$(P$1+2),XH$(P$1+2)

58 36 RELEASE PROC4

59 37 TRANSFER,FINAL

60 38 PROD4 QUEUE MEM5

61 39 SEIZE PROC5

62 40 DEPART MEM5

63 41 ADVANS X$(P$1+2),XH$(P$1+2)

64 42 RELEASE PROC5

65 43 FINAL TERMINATE

66 44 GENERATE 4000

67 45 TERMINATE 1

68 START 1

69 END

SYMBOL VALUE SYMBOL VALUE

====== ===== ====== =====

BUF 9 FINAL 43

MEM1 1 MEM2 2

MEM3 2 MEM4 3

MEM5 4 PROC1 1

PROC2 2 PROC3 3

PROC4 4 PROC5 5

PROD1 18 PROD2 24

PROD3 31 PROD4 38

VBUF 1

RELATIVE CLOCK 4000 ABSOLUTE CLOCK 4000

BLOCK COUNTS

BLOCK CURRENT TOTAL BLOCK CURRENT TOTAL BLOCK CURRENT TOTAL

1 1 167 2 0 166 3 0 166

4 1 168 5 0 167 6 0 167

7 1 167 8 0 166 9 0 499

10 0 499 11 0 213 12 0 213

13 0 213 14 0 213 15 1 213

16 0 212 17 0 212 18 0 286

19 0 286 20 0 286 21 0 286

22 1 286 23 0 285 24 0 497

25 0 11 26 0 11 27 0 11

28 0 11 29 0 11 30 0 11

31 0 486 32 0 199 33 0 199

34 0 199 35 1 199 36 0 198

37 0 198 38 0 287 39 0 287

40 0 287 41 1 287 42 0 286

43 0 495 44 1 2 45 0 1

FACILITY AVERAGE NUMBER AVERAGE SEIZING PREEMPTING

UTILIZATION ENTRIES TIME/TRAN TRANS.NO. TRANS.NO.

1 0.74 213 13.93 5

2 1.00 286 13.96 8

3 0.04 11 14.18

4 0.70 199 14.03 10

5 0.98 287 13.64 2

STORAGE CAPACITY AVERAGE AVERAGE ENTRIES AVERAGE CURRENT MAXIMUM

CONTENT UTILIZ. TIME/TR CONTENT CONTENT

1 10 0.00 0.00 213 0.66 0 1

2 10 0.00 0.07 286 9.40 0 1

QUEUE MAXIMUM AVERAGE TOTAL ZERO PERC. AVERAGE $AVERAGE TABLE CURRENT

CONTENT CONTENT ENTRIES ENTRIES ZERO TIME/TR TIME/TR NUMBR CONTENT

1 2 0.71 499 165 33.07 5.67 8.47 0

2 1 0.01 11 9 81.82 2.45 13.50 0

3 1 0.08 199 138 69.35 1.70 5.56 0

4 1 0.57 287 25 8.71 7.89 8.64 0

5. Заключение

В заключении приведём анализ файла отчёта, содержащего всю необходимую информацию о результатах моделирования и статистические данные о работе всех узлов схемы.

1. Сначала определим необходимые для нормальной работы объёмы буферов.

Буфер системы должен иметь объём не менее: 2 у.е. памяти*;

Буферы второго сегмента должны иметь объём не менее: 1 у.е. памяти;

*1 у.е. памяти в нашем случае равна объёму одного транзакта.

2. Основные данные о работе очередей:

Очередь к буферу первого микропроцессора:

- максимальное содержимое: 1 транзакт;

- среднее содержимое: 0 транзактов;

- среднее время пребывания в очереди: 0,66 мкс;

Очередь к буферу второго микропроцессора:

- максимальное содержимое: 1 транзакт;

- среднее содержимое: 0,07 транзакта;

- среднее время пребывания в очереди: 9,4 мкс.

Очередь к буферу третьего микропроцессора:

- максимальное содержимое: 1 транзакт;

- среднее содержимое: 0,01 транзакта;

- среднее время пребывания в очереди: 2,45 мкс.

Очередь к буферу четвёртого микропроцессора:

- максимальное содержимое: 1 транзакт;

- среднее содержимое: 0,08 транзакта;

- среднее время пребывания в очереди: 1,7 мкс.

Очередь к буферу пятого микропроцессора:

- максимальное содержимое: 1 транзакт;

- среднее содержимое: 0,57 транзакта;

- среднее время пребывания в очереди: 7,89 мкс.

Очередь на обработку(VBUF):

- максимальное содержимое: 2 транзакт;

- среднее содержимое: 0,71 транзакта;

- среднее время пребывания в очереди: 5,76 мкс. |